GL9767

Overview

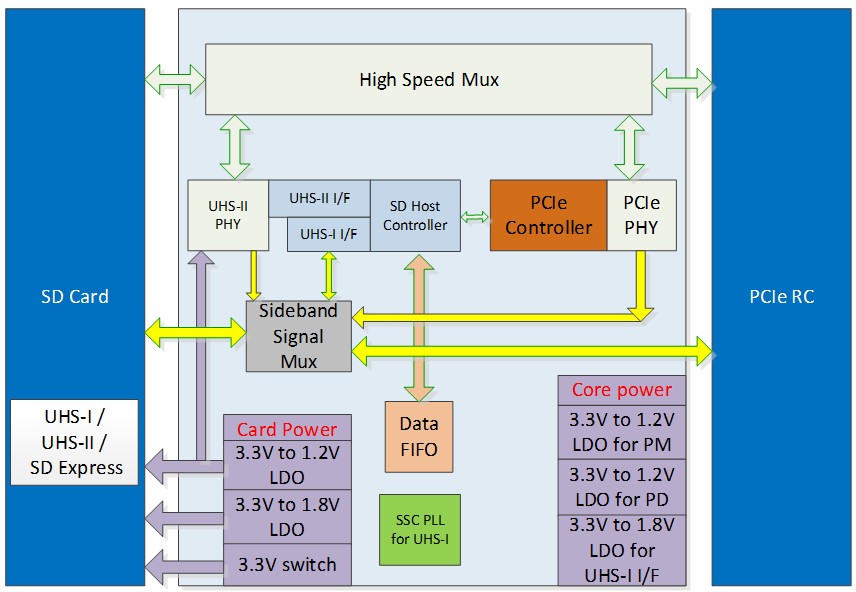

GL9767 is a PCI Express Rev. 2.1 compliant card reader controller which integrates PCI Express PHY, UHS-II PHY, memory card access interface, regulators (3.3V-to-1.8V and 3.3V-to-1.2V) and card power switch.

GL9767 supports various types of SD memory cards, such as Secure DigitalTM (SD), SDHC, miniSD and microSD (T-Flash). It supports high density memory cards (Capacity up to 128TB), such as SDXC and SDUC and ultra high speed memory cards, SD 3.0 UHS-I, SD 4.0 UHS-II and the latest generation high speed memory cards, SD 7.1 Express card and SD 8.0 Express card.

GL9767 supports PCI Express ASPM, L1 sub-states, Runtime D3 (RTD3 Hot/Cold), Latency Tolerance Reporting (LTR), and Optimized Buffer Flush/Fill (OBFF) for saving power consumption.

- Compliant with PCI Express Base Specification Rev. 2.1

- Support 1-Lane 2.5 / 5.0 / 8.0 / 16 GT/s PCI Express Bus

- Compliant with SD Specifications Part 1 Physical Layer Specification Version 8.00

- Compliant with SD Specifications Part 1 Physical Layer Specification Version 7.10

- Compliant with SD Specifications Part A2 SD Host Controller Standard Specification Version 4.20

- Supported memory card interfaces:

- Secure Digital TM (SD), SDXC, SDHC, SDUC

- SD 7.1 Express mode up to 985MB/sec

- SD 6.0 Application Performance Class A2

- SD 5.0 Application Performance Class A1 and Video Speed Class

- SD 4.0 UHS-II FD/HD mode up to 312MB/sec

- SD 3.0 UHS-I DDR-225 (225MHz SD clock), SDR-104 (208MHz SD clock), SDR-50 (100MHz SD clock) and DDR-50 (50MHz SD clock)

- Support SanDisk high-performance Extreme Pro SDXC UHS-I Card up to 200MB/s

- Optional: SD 8.0 Express mode (PCIe Gen.3 x 2 or Gen.4 x 1 or Gen.4 x 2 ) up to 3940MB/s

- MMC 4-bit date mode

- Support PCI Express Clock Request (CLKREQ_N)

- Support PCI Express ASPM L0s / L1

- Support PCI Express L1 sub-states (L1.1 and L1.2) and RTD3 (Runtime D3 hot/cold)

- Support PCI Express LTR (Latency Tolerance Reporting) and OBFF (Optimized Buffer Flush/Fill)

- Support Modern Standby for Windows OS.

- Support S0ix for Chrome OS and Linux OS.

- High efficiency hardware DMA engine to improve data transfer performance

- On-chip 3.3V to 1.2V regulator for core and analog macros

- On-chip 3.3V to 1.8V regulator for SD 4.0 / SD Express card power VDD2 (600 mA)

- On-chip 3.3V power switch for SD card power (800 mA)

- Support Over-current protection mechanism

- Support Spread Spectrum Clock (SSC) for SD to reduce EMI effect

- Available in QFN32 5mm x 5mm package

- SD Express / UHS-II Verification Program (SVP) Verified Product by SD Association

- System requirement

- The PCIe root port need to support and enable PCIe native hot plug

- BIOS need to support PCIe hot plug relative options